# High-Performance Monolayer WSe<sub>2</sub> p/n FETs via Antimony-Platinum Modulated Contact Technology towards 2D CMOS Electronics

Ang-Sheng Chou<sup>1+\*</sup>, Yu-Tung Lin<sup>1,3+</sup>, Yuxuan Cosmi Lin<sup>2</sup>, Ching-Hao Hsu<sup>1,3</sup>, Ming-Yang Li<sup>1</sup>, San-Lin Liew<sup>4</sup>, Sui-An Chou<sup>1</sup>, Hung-Yu Chen<sup>2</sup>, Hsin-Yuan Chiu<sup>1,5</sup>, Po-Hsun Ho<sup>1</sup>, Ming-Chun Hsu<sup>3</sup>, Yu-Wei Hsu<sup>3</sup>, Ning Yang<sup>2</sup>, Wei-Yen Woon<sup>6</sup>, Szuya

Liao<sup>6</sup>, Duen-Huei Hou<sup>4</sup>, Chao-Hsin Chien<sup>5</sup>, Wen-Hao Chang<sup>7</sup>, Iuliana Radu<sup>1</sup>, Chih-I Wu<sup>3</sup>, H.-S. Philip Wong<sup>1</sup> and Han Wang<sup>2\*</sup>

<sup>1</sup>Corporate Research, TSMC, Hsinchu, Taiwan; <sup>2</sup>Corporate Research, TSMC, San Jose, CA, USA; <sup>3</sup>Graduate Institute of Photonics and Optoelectronics, NTU, Taipei, Taiwan; <sup>4</sup>Quality & Reliability, TSMC, Hsinchu, Taiwan; <sup>5</sup>Institute of Electronics, NYCU, Hsinchu, Taiwan; <sup>6</sup>Pathfinding, TSMC, Hsinchu, Taiwan; <sup>7</sup>Department of Electrophysics, NYCU, Hsinchu, Taiwan <sup>+</sup>Both authors contributed equally; \*Email: aschoua@tsmc.com, hanwang@tsmc.com

Abstract - Low resistance contact technology for 2D semiconductors is a key bottleneck for the practical application of 2D channel materials at advanced logic nodes. This work presents a novel Sb-Pt modulated contact technology which can alleviate the Fermi-level pinning effect and mediate the band alignment at the metal-2D semiconductor interface, leading to exceptional ohmic contacts for both p-type and n-type WSe<sub>2</sub> FETs (p/n FET). WSe<sub>2</sub> FETs with different Sb/Pt contact compositions, in combination with new oxide-based encapsulation/doping technologies, exhibits record low pFET contact resistance of 0.75 k $\Omega$ ·µm among all reported monolayer (1L) 2D pFETs. The nFET contact resistance of 1.8 k $\Omega$ ·µm is also the lowest among 1L WSe<sub>2</sub> nFETs. Both 1L WSe<sub>2</sub> pFET and nFET demonstrated remarkable on-state p/n current ~150  $\mu$ A/ $\mu$ m at |V<sub>D</sub>|=1 V, indicating the potential of WSe<sub>2</sub> for CMOS applications. A new version of the semi-automated dry transfer process for chemical vapor deposition (CVD) WSe<sub>2</sub> was also developed utilizing a novel Bi/PMMA/TRT support stack, offering low defect wrinkle-free WSe2 transfer at wafer-scale.

# I. INTRODUCTION

2D semiconducting transition metal dichalcogenides (TMD) are promising as atomically thin channel materials for future post-silicon CMOS transistor technology at the ultimate scale [1]. However, achieving low resistance contact for 2D semiconductor p/n FETs remains a crucial challenge towards such technology insertion at advanced technology nodes. Recent development of semimetallic contacts (e.g. Bi [2] and Sb [3]) as well as low-melting-point metal contacts (e.g. Sn and In) [4] have demonstrated reduction in contact resistance (R<sub>C</sub>) and good performance for nFETs. However, the performances of pFETs made with TMDs are still one to two orders of magnitude lower, because these proposed contact metals for TMD nFETs have improper band alignments for hole conductions, leading to high Schottky barrier (SB), high R<sub>C</sub> and poor current-delivery capability. WSe<sub>2</sub> has been proposed as a promising TMD with ambipolar conduction characteristics, and the recent development of reliable and scalable synthesize and transfer technologies for TMDs, including monolayer WSe2, have paved the way towards practical applications. In this work, we develop a contact modulation technology based on Sb-Pt stacked deposition, which can relieve the Fermi-level pinning effect and offers work function tuning with different chemical compositions. This technology, in combination with proper channel capping layers, gives rise to low R<sub>C</sub> for both electron and hole conductions towards enabling high performance CMOS technologies based on monolayer CVD WSe2. The key contributions of this work are four-folds: (i) a new version of semiautomated wafer-scale low defect transfer process based on Bi interfacial layers and PMMA/TRT support layer is demonstrated; (ii) Sb semimetal is mixed with high work function metal Pt as a modulated contact technology for monolayer WSe2, which enables low R<sub>C</sub> for both pFETs and nFETs; (iii) new MoO<sub>x</sub> and SiON<sub>x</sub>

channel capping/doping technologies are developed for 1L WSe<sub>2</sub> pFET and nFET, respectively, to further boost the device performance. (iv) The proposed device technologies have led to hysteresis-free I-V characteristics, low SB heights close to thermal voltage at room temperature, record low R<sub>c</sub> value down to 0.75 k $\Omega$ ·µm and 1.8 k $\Omega$ ·µm and high on-state current of 151 µA/µm and 147 µA/µm, for 1L WSe<sub>2</sub> pFETs and nFETs, respectively.

# II. APPROACH

#### A. Bi-Assisted Dry Transfer of Wafer-Scale WSe<sub>2</sub>

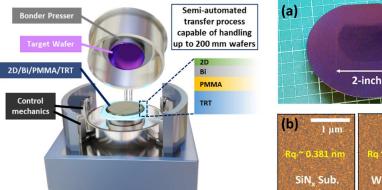

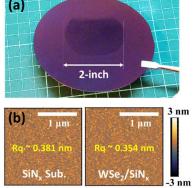

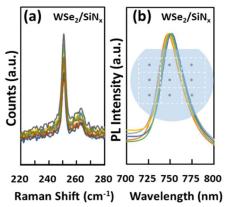

Throughout this study, 1L WSe<sub>2</sub> was used as the channel material, grown by CVD. CVD-1L-WSe<sub>2</sub> was transferred onto 100 nm SiN<sub>x</sub>/Si substrates by a new version of the bismuth (Bi)-assisted dry transfer technology that we previously developed in-house [5], with novel modifications using a new Bi/PMMA/TRT interfacial stack (schematic shown in Fig. 1). This semi-automated transfer process utilizes the weakly coupled interface between semimetal Bi and WSe<sub>2</sub> to minimize the introduction of additional defects during the transfer process, while the new PMMA/TRT support stack offers balanced adhesion property and mechanical flexibility to achieve wrinkle-free transfer at large wafer-scale. Atomic force microscopy (AFM, Fig. 2b), and Raman spectrum/photoluminescence (PL) (Fig. 3) were conducted to characterize the surface cleanliness, roughness, and uniformity of the material before and after the transfer process.

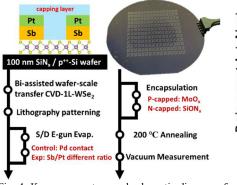

## B. Devices Fabrication and Charecterization

As described in Fig. 4, after dry-transfer, Helium-ion-beam lithography was used to pattern the S/D contact electrodes. Sb with different thicknesses and Pt capping layers were deposited by e-beam evaporation and followed by lift-off to form the contact electrodes. Then  $MoO_x$  and  $SiON_x$  were deposited on top as the encapsulating layers, to achieve almost hysteresis-free pFET and nFET, respectively. The I-V characteristics were measured in vacuum system with Keysight B1500A parameter analyzer. Raman spectra was utilized to examine the interface coupling between the contact metal and WSe<sub>2</sub>, and energy-dispersive X-ray spectroscopy (EDS) in a scanning transmission electron microscope (STEM) was used to reveal chemical compositions at the contact interfaces.

## **III. RESULTS**

# A. Sb-Pt Contact Engineering for WSe<sub>2</sub> p/n FETs

WSe<sub>2</sub> with semimetal contact such as Bi has shown promising nFET device characteristics. To reduce the contact resistance and achieve better WSe<sub>2</sub> pFET performance, it is critical to identify contact metals with appropriate work functions and weaker Fermilevel pinning effect because of metal-induced gap sates (MIGS). We discover that by mixing thin layer semimetal Sb with the highwork-function metal Pt, both issues can be effectively addressed, which offers improved contact and better on-state performance for both nFETs and pFETs made with monolayer WSe<sub>2</sub>.

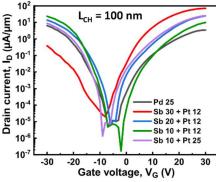

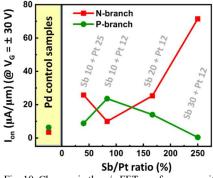

Fig. 5 summarizes typical transfer  $(I_D-V_G)$  characteristics of pristine short-channel ( $L_{CH} = 100$  nm) WSe<sub>2</sub> FETs with different Sb and Pt compositions and with Pd contact as the baseline device. Pd is selected as the control material throughout this study because direct deposition of pure Pt on WSe<sub>2</sub> is known to suffer from adhesion issue, and Pd has similar work function as Pt and can serve as good reference. Depending on the Sb-to-Pt ratio, either p-branch current or n-branch current is improved by one and two orders of magnitude, respectively, as compared to the Pd-contact device. It is observed that device with thinner Sb on WSe<sub>2</sub> shows stronger pFET behavior, whereas device with thicker Sb exhibits nFET behavior.

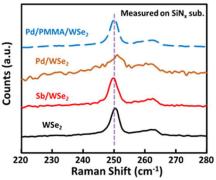

We believe that the Sb-Pt contact plays two vital roles in achieving such improved pFET and nFET performance. First, the insertion of Sb provides a buffer layer in between WSe<sub>2</sub> and the high-work-function Pt metal, which minimizes lattice damage to WSe<sub>2</sub> during Pt metal deposition, and alleviates the metal-WSe<sub>2</sub> interactions. To confirm this effect, Sb/WSe2 and Pd/WSe2 reference heterostructure samples are prepared for Raman spectroscopy measurements [6], and the results are presented in Fig. 6. The Raman characteristic peak of WSe2 becomes wider and much weaker after 1.5 nm Pd is deposited on top. The Pd/PMMA/WSe<sub>2</sub> sample displays a similar Raman intensity to the pristine WSe<sub>2</sub> sample, ruling out the possibility that 1.5 nm Pd may block the incident light and attenuate the local light field on WSe2 during the Raman spectroscopy measurement. Hence, some level of disruption of the WSe<sub>2</sub> lattice is induced after the deposition of conventional high work-function metals such as Pd, possibly through defect introduction or interfacial chemical bonding. Both effects can lead to severe Fermi-level pinning effects, including defect induced gap states (DIGS) and MIGS. By contrast, the Raman peak of Sb/WSe2 sample do not exhibit any intensity or width change, indicating less disruption caused to the WSe2 lattice by semimetal Sb than Pd.

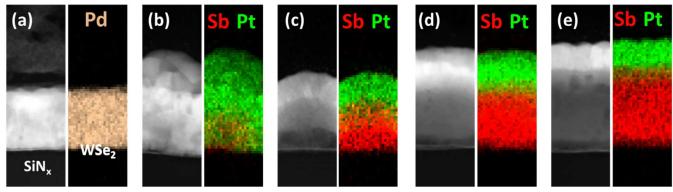

Second, the interfacial properties, especially the effective work functions at the Sb-Pt/WSe2 interfaces can be modulated by the Sbto-Pt ratio, which contributes to the nFET-to-pFET conversion. Cross-sectional STEM images and the corresponding EDS mappings on the Sb/Pt contact regions of WSe2 FETs are shown in Fig. 7. It is worth noting that partial re-sublimation of Sb may take place during the Pt evaporation because of heating, resulting in slightly smaller thickness of the actual Sb layers than the target deposition thickness. Another interesting observation is that mixing between Sb and Pt may occur at the metal/WSe<sub>2</sub> interface especially when thinner Sb (10 nm) is deposited (Fig. 7 b and c). The Sb-Pt mixing can modulate its effective work function, and thus the contact barrier at the metal/WSe2 interface. Note that the work function of pristine Sb and Pt are 4.4 eV and 5.6 eV, respectively, and the Sb-Pt mixed layer could have an effective work function in between, which can result in the polarity modulation of the WSe<sub>2</sub> FETs when the deposition thickness of Sb changes.

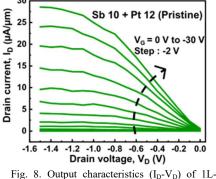

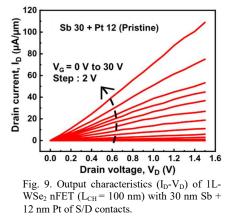

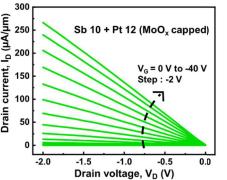

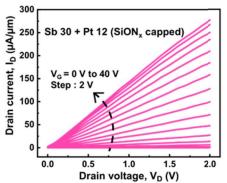

Fig. 8 and 9 show the output  $(I_D-V_D)$  characteristics of the best nFET and pFET for pristine WSe<sub>2</sub> with Sb 10 nm/Pt 12 nm and Sb 30 nm/Pt 12 nm as the contact electrodes, respectively. The relationship between the p-branch and n-branch on-currents and the different Sb/Pt compositions are summarized in Fig. 10.

#### B. p/n FET Performance Boosting with Channel Modulation

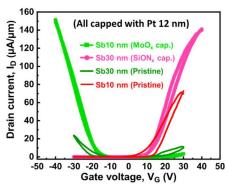

To further boost the on-state current for both the pFETs and the nFETs, we capped the WSe<sub>2</sub> channels with different dielectric layers: 10 nm  $MoO_x$  deposited by e-beam evaporation for pFETs, and 30 nm  $SiON_x$  deposited by atomic layer deposition (ALD) for nFETs. The presence of capping layers leads to two beneficial impacts: (i)

interface trap states passivation, and (ii) modulation doping. First, the capping layers are able to neutralize the trap states, making the device characteristics almost hysteresis-free (Fig. 11). Second, modulation doping as well as an enhancement of on-state currents can be induced by the  $MoO_x$  and  $SiON_x$  capping layer for pFET and nFET, respectively.

After Sb-Pt contact engineering and capping layer engineering, we report high-performance I-V characteristics for both nFET and pFET with monolayer WSe<sub>2</sub>. The output characteristics for the 1L WSe<sub>2</sub> pFET and nFET are shown in Fig. 12 and Fig. 15, respectively. The on-state current for pFET (contact metal: 10 nm Sb/12nm Pt; capping: 10 nm MoO<sub>x</sub>) is 151  $\mu$ A/ $\mu$ m (V<sub>D</sub> = -1 V) and the on-state current for nFET (contact metal: 30 nm Sb/12nm Pt; capping: 30 nm SiON<sub>x</sub>) is 147  $\mu$ A/ $\mu$ m (V<sub>D</sub> = 1 V).

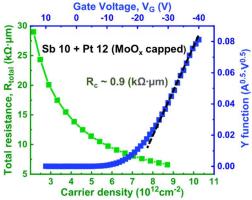

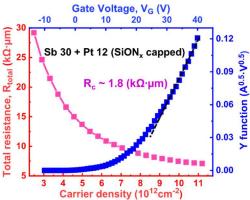

#### C. Contact Resistance and Schottky Barrier Height

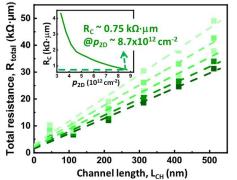

Both Y-function method (YFM) and transfer-length method (TLM) are used to estimate the contact resistances of the optimized 1L WSe<sub>2</sub> pFET and nFET (Fig. 13, 14, and 16). According to YFM, the contact resistances  $R_C$  are extracted to be  $0.9 \text{ k}\Omega \cdot \mu m$  for the pFET with MoO<sub>x</sub> capping, and 1.8 k $\Omega \cdot \mu m$  for the nFET with SiON<sub>x</sub> capping. In addition, we also employ the TLM method for the pFET to give a more accurate  $R_C$  extraction since YFM method typically tends to overestimate the contact resistance. Using TLM, the contact resistance is extracted to be 0.75 k $\Omega \cdot \mu m$  for the 1L WSe<sub>2</sub> pFET.

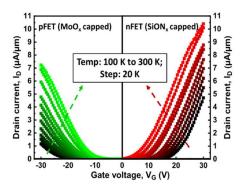

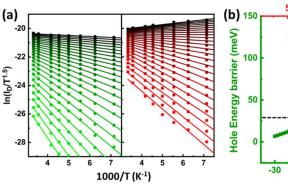

To extract the Schottky barrier heights  $\Phi_{SB}$  at the p-type and ntype contacts of the p/n FETs, transfer characteristics are measured at different temperatures (from 100 K to 300 K), as plotted in Fig. 17. It is observed that the drain currents for both the pFET and the nFET decrease at lower temperature, which suggest that the transport characteristics for both devices are dominated by the  $\Phi_{SB}$  at the metal contacts.  $\Phi_{SB}$  can be extracted by finding the slopes of the Arrhenius plots (ln(I<sub>D</sub>/T<sup>1.5</sup>) versus 1/T) as shown in Fig. 18 (a). The  $\Phi_{SB}$  as functions of the gate voltage for the pFET and the nFET are summarized in Fig. 18 (b), which is the comprehensive result after considering the barrier width change caused by doping effect. Using this novel Sb-Pt modulated contact technology, the contact barriers are small for both pFET and nFET at room temperature.

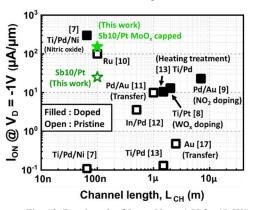

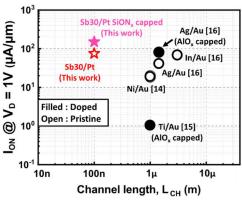

#### D. Benchmark

Fig. 19 and 20 benchmark the  $I_{ON}$  as a function of channel length among our work and previous studies of monolayer CVD and exfoliated WSe<sub>2</sub> FETs [7-17]. The on-state current for both our pFET and nFET are among the highest reported in the literature with the nFET current being record value among CVD 1L WSe<sub>2</sub> nFET. Our reported pFET R<sub>C</sub> is the lowest among all monolayer 2D pFETs while the nFET R<sub>C</sub> is also the lowest among 1L CVD WSe<sub>2</sub> nFETs, as shown in Fig. 21. These devices exhibit high performance and low contact resistance with minimal hysteresis for both pFETs and nFETs, and are hence a promising technology for developing WSe<sub>2</sub> FETs toward 2D CMOS electronics for advanced logic.

ACKNOWLEDGMENT: AFM was supported by Taiwan Instrument Research Institute. Helium-ion beam lithography was supported by TSMC-NTU Joint Research Center and Ministry of Science and Technology (Grant No. MOST 110-2622-8-002-014).

REFERENCES: [1] Q. Cheng, et al., *InfoMat.*, 2, 4, 656 (2020). [2] P.-C. Shen, et al., *Nature*, 593, 211 (2021). [3] A.-S. Chou, et al., *IEDM*, 7.2.1 (2021). [4] A. Kumar, et al., *IEDM*, pp. 7.3.1 (2021). [5] M.-Y. Li, et al., *VLSI*, T1-5 (2022). [6] W. Yalon, et al., *Nano Lett.*, 17, 6, 3429 (2017). [7] C.-C. Chiang, et al., *IEEE EDL*, 43, 2, 319 (2022). [8] M. Yamamoto, et al., *Nano Lett.*, 16, 4, 2720 (2016). [9] P. Zhao, et al., *ACS Nano*, 8, 10, 10808 (2014). [10] K. Maxey, et al., *Nature*, 568, 70 (2019). [13] B. Liu, et al., *ACS Nano*, 10, 5, 5153 (2016). [14] S. Rai, et al., *JAP*, 131, 094301 (2022). [15] C.-S. Pang, et al., *Small*, 15, 41, 1902770 (2019). [16] W. Liu, et al., *Nano Lett.*, 13, 5, 1983 (2013). [17] L. Kong, et al., *Nat. Comm.*, 11, 1866 (2020).

Fig. 1. Schematic of the Bi-assisted semi-auto transfer facility capable of handling up to 200 mm wafers. The technology is further improved in this work by using thermal release tape (TRT) and PMMA to enhance transfer quality.

Fig. 4. Key process steps and schematic diagram of the back-gated CVD 1L-WSe2 device fabrication with contact metal and encapsulation splits. Photo of the wafer after device fabrication is also shown.

Fig. 2. (a) Photograph of 2" CVD-1L-WSe<sub>2</sub> transferred on 4" SiN<sub>x</sub> (100 nm)/p<sup>++</sup>-Si wafer. (b) AFM images of the SiNx/Si substrate alone and after WSe<sub>2</sub> film is transferred, showing comparable surface roughness.

Fig. 5. Transfer characteristics (I<sub>D</sub>-V<sub>G</sub>) of the Pdcontacted and different compositions of Sb/Ptcontacted 1L-WSe<sub>2</sub> FETs at  $|V_D| = 1V$ . The device characteristics without encapsulation are ambipolar.

Fig. 3. (a) Raman and (b) PL spectra of the transferred WSe2 on SiNx/Si substrate, showing uniform Raman and PL peak positions at all nine locations of the 2" region in Fig. 2(a), demonstrating the uniform quality of the transferred WSe<sub>2</sub> material.

Fig. 6. Raman spectra of pristine 1L-WSe<sub>2</sub>, and those capped with 1.5 nm Sb, Pd, and Pd/PMMA. WSe<sub>2</sub> Raman peak becomes distorted in the sample directly capped with Pd, but remains intact in the Sb capped sample.

Fig. 7. High resolution cross-sectional STEM images and EDS mapping of (a) Pd. Pd is selected as the control p-type contact material because direct deposition of pure Pt on WSe2 is known to suffer from adhesion issue, and Pd has similar work function as Pt and can serve as good reference, and (b-e) different compositions of Sb/Pt contacted on 1L CVD WSe2. Note: (b) 10 nm Sb with 25 nm Pt, (c) 10 nm Sb with 12 nm Pt, (d) 20 nm Sb with 12 nm Pt, (e) 30 nm Sb with 12 nm Pt. Thinner Sb intermixes more vigorously with Pt, resulting in more complete alloying of Sb and Pt.

WSe<sub>2</sub> pFET ( $L_{CH}$  = 100 nm) with 10 nm Sb + 12 nm Pt of S/D contacts.

Fig. 10. Changes in the p/n FETs performance with different contact compositions. 10 nm Sb + 12 nm Pt contact gives the best pFET performance.

Authorized licensed use limited to: The University of Hong Kong Libraries. Downloaded on May 10,2024 at 02:48:28 UTC from IEEE Xplore. Restrictions apply.

Fig. 11. Transfer characteristics  $(I_D-V_G)$  of the Sb/Pt-1L-WSe<sub>2</sub> FET  $(L_{CH} = 100 \text{ nm})$  at  $|V_D| = 1 \text{ V}$ , before and after  $MoO_x$  (Green) and  $SiON_x$  (Pink) encapsulation.

Fig. 14. Extraction of  $R_C$  by TLM analysis for the MoO<sub>x</sub> capped 1L WSe<sub>2</sub> pFET with carrier density modulated by the gate.  $R_C = 0.75 \text{ k}\Omega$ ·µm is extracted at carrier density  $p_{2D} \sim 8.7 \text{x} 10^{12} \text{ cm}^{-2}$ .

Fig. 17. Temperature-dependent measurement of pFET (Green) and nFET (red). The current levels in both devices decrease at lower temperature.

Fig. 19. Benchmark of  $I_{ON}$  at  $V_D = -1$  V for 1L WSe<sub>2</sub> pFETs. The open and filled symbols are pristine and doped samples, respectively.

Fig. 12. Output characteristics  $(I_D-V_D)$  corresponding to bright-green-line in Fig. 11, i.e. Sb/Pt:10/12 nm after MoO<sub>x</sub> capping.

Fig. 15. Output characteristics  $(I_D-V_D)$  corresponding to the pink-line in Fig. 11, i.e. Sb/Pt:30/12 nm after SiON<sub>x</sub> capping.

Fig. 13. Extraction of contact resistance by Y-function method for the Sb10Pt12-WSe<sub>2</sub>-pFET after  $MoO_x$  capping.

Fig. 16. Extraction of contact resistance by Y-function method for the Sb30Pt12-WSe<sub>2</sub>-nFET after SiON<sub>x</sub> capping.

(b) 150 (c) 15 (c) 25 (c) 25 (c) 150 (c) 150(c)

Fig. 18. (a) Arrhenius plots of  $MoO_x$ -capped-pFET (green) and  $SiON_x$ -capped-nFET (red) at different gate overdrive ( $|V_G|$  from 6 to 30 V, in step of 1 V). (b) The energy barrier of pFET (green) and nFET (red) are close to be negligible at room temperature.  $k_B$  is Boltzmann constant.

Fig. 20. Benchmark of  $I_{ON}$  at  $V_D = 1 V$  for 1L WSe<sub>2</sub> nFETs. The open and filled symbols are pristine and doped samples, respectively.

1L-WSe<sub>2</sub>-pFET [11] Transfer-Pd/Au ; w/o doping; 50 k $\Omega$ · $\mu$ m Ru w/o doping; 2.7 kΩ·µm [10] [9] Pd/Au NO2 doping; 1.3 kΩ·µm [8] Ti/Pt WO<sub>x</sub> doping; 1.5 k $\Omega$ · $\mu$ m [7] Ti/Pd/Ni Nitric Oxide doping; 0.95 kΩ·μm This MoO<sub>x</sub> capped; 0.75 kΩ·μm Sb10/Pt worl 1L-WSe2-nFET [12] 17 kΩ·µm 7.5 kΩ·µm [16] 6.5 kΩ·µm [16] Thi SiON, capped; 1.8 kΩ·μm work 1 10 0.1 100  $R_{c}$  (k $\Omega \cdot \mu m$ )

Fig. 21. Comparison of contact resistance for 1L WSe<sub>2</sub> p/n-FETs with respect to different contact approaches reported in the literature.